FAQ专区

搜索

-

大类:

-

小类:

已选条件:

移除所有

-

徐玉栋2023-07-20 08:44:49您好,我想问一下你们有没有实现光纤传输的一个芯片呢?官方回复:

徐玉栋2023-07-20 08:44:49您好,我想问一下你们有没有实现光纤传输的一个芯片呢?官方回复:您好,我们的PH1A90, PH1A100, PH1A180, PH1A400等有SERDES的器件都可以用于光口传输。

-

Xuebing2023-07-19 23:10:40TD 5.6.2 没有指导书上的擦除内部flash选项,烧写内部flash也无法正常操作官方回复:

Xuebing2023-07-19 23:10:40TD 5.6.2 没有指导书上的擦除内部flash选项,烧写内部flash也无法正常操作官方回复:您好,对于ELF2系列的器件您可以下载一个4.6.6版本的软件,4.6.X系列的软件对于小器件开发更好用。

-

bobo2023-07-18 13:03:40EF3芯片的加载模式msel是通过管脚配置吗?手册里没有找到对应的pin定义官方回复:

bobo2023-07-18 13:03:40EF3芯片的加载模式msel是通过管脚配置吗?手册里没有找到对应的pin定义官方回复:您好,我们的EF3系列芯片的加载模式是通过位流设置,在TD软件中设置加载模式,然后生成相应的位流,下载到EF3的FLASH中,器件在启动时首先读取FLASH中设置加载模式的部分,然后转到相应的加载模式。

-

KevinLiu2023-07-14 14:18:51SF1 RISCV内核的上电启动时间是否可以加快呢? 目前 RISCV 100M时钟下运行上电时间需要200ms,我们希望小于20ms官方回复:

KevinLiu2023-07-14 14:18:51SF1 RISCV内核的上电启动时间是否可以加快呢? 目前 RISCV 100M时钟下运行上电时间需要200ms,我们希望小于20ms官方回复:您好,可以通过修改MSPI的加载时钟频率,同时将MSPI设置为X4模式。这样可以将FPGA的加载时间缩短到10-20ms之间。

-

孙涛2023-07-06 11:25:35EF2L45LG144B这款FPGA的HSWAPEN引脚是多少脚,手册上没有写明,对程序烧录期间的引脚电平有要求官方回复:

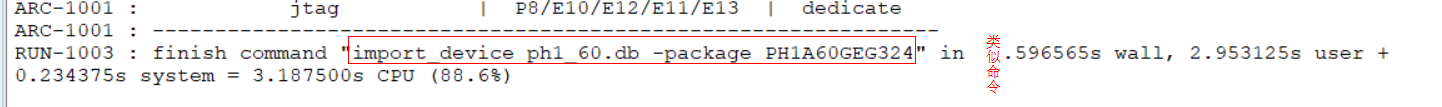

孙涛2023-07-06 11:25:35EF2L45LG144B这款FPGA的HSWAPEN引脚是多少脚,手册上没有写明,对程序烧录期间的引脚电平有要求官方回复:您好,我们的EF2 EF3器件的HSWAPEN不是通过物理引脚设置的,是放在位流的最前面设置生效的,所以该配置需要通过TD软件的property选项设置,如下:

-

林毅2023-07-05 17:58:34请问EF2的ADC参考电压,在ip generator中如果不勾选,该引脚用做GPIO或者是不接,ADC能否正常工作?官方回复:

林毅2023-07-05 17:58:34请问EF2的ADC参考电压,在ip generator中如果不勾选,该引脚用做GPIO或者是不接,ADC能否正常工作?官方回复:您好,如果使用ADC则需要沟选此引脚,且在该引脚的外部接上对应的参考电压,否则ADC是无法正常工作的。

-

李世科2023-07-04 14:35:02SDK里面的MCUl工程都是SRAM运行模式,只支持最大16k的代码量。

李世科2023-07-04 14:35:02SDK里面的MCUl工程都是SRAM运行模式,只支持最大16k的代码量。

我想切换到flash运行模式,需要修改哪些keil工程配置项?软件代码需要做哪些调整?官方回复: -

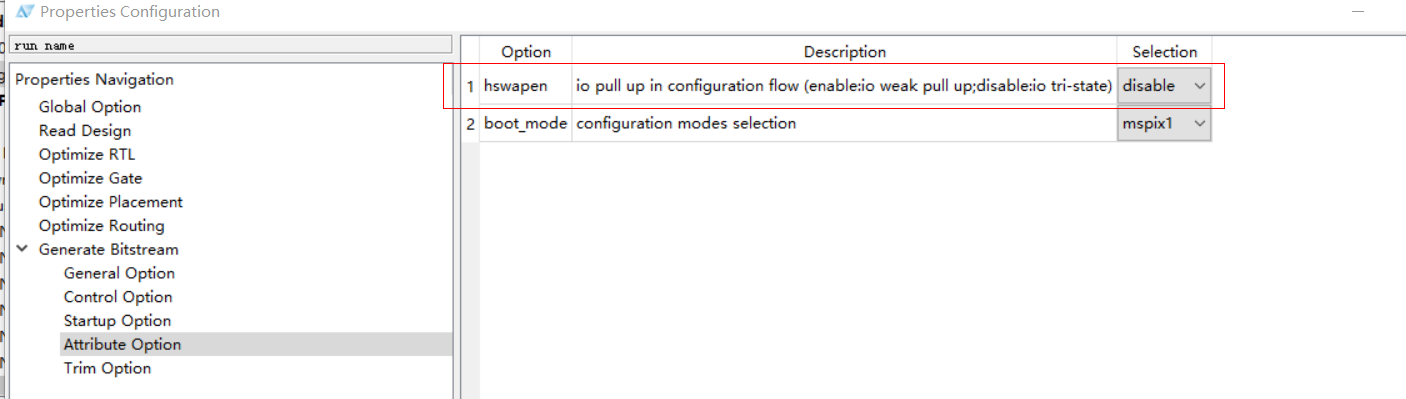

刘新宇2023-07-04 11:08:48请问TD软件是否能以命令行的方式实现下载功能?官方回复:

刘新宇2023-07-04 11:08:48请问TD软件是否能以命令行的方式实现下载功能?官方回复:您好,可以的,您可以参考TD软件UG,通过命令行形式启动TD软件,具体的下载命令可以从界面执行后,参考从console复制相应命令从命令行执行。