FAQ专区

搜索

-

大类:

-

小类:

已选条件:

移除所有

-

闫茹2025-01-10 11:46:34您好,我想问下,在modelsim里面仿真Anlogic ip(rom)时,怎样添加可以使modelsim正确读出rom的初始化文件(.dat)文件?官方回复:

闫茹2025-01-10 11:46:34您好,我想问下,在modelsim里面仿真Anlogic ip(rom)时,怎样添加可以使modelsim正确读出rom的初始化文件(.dat)文件?官方回复:可以使用函数readmemh,仿真IP时,IP中附带的文件也需仿真仿真目录中。

-

尤思远2025-01-06 10:16:28请问EF3L90CG400B,在TD 4.6.7中,如何设置4个JTAG配置管脚(TCK、TMS、TDI和TDO)为普通IO?官方回复:

尤思远2025-01-06 10:16:28请问EF3L90CG400B,在TD 4.6.7中,如何设置4个JTAG配置管脚(TCK、TMS、TDI和TDO)为普通IO?官方回复:在TD打开的工程,左上角,device setting中有对应的dual purpose pins对JTAG进行设置

-

shikang li2023-12-19 16:49:52第一次使用安路fpga,芯片型号:EG4X20BG256,不知道如何将双端lvds信号转成单端信号?或者将单端信号转成lvds双端输出信号?官方回复:

shikang li2023-12-19 16:49:52第一次使用安路fpga,芯片型号:EG4X20BG256,不知道如何将双端lvds信号转成单端信号?或者将单端信号转成lvds双端输出信号?官方回复:你好,

ADC文件里IO位置只需要约束P端位置,RTL代码里input/output端口只需要例化P端。

例如:

RTL里例化:

input wire rx_lvds_d_p,

ADC文件里指定位置:

set_pin_assignment { rx_lvds_d_p } { LOCATION = B2; IOSTANDARD = LVDS33; }

-

李晓2023-12-11 11:03:07请问,这个开发板(EG4X20-MINI-DEV)的原理图还有吗?官方回复:

李晓2023-12-11 11:03:07请问,这个开发板(EG4X20-MINI-DEV)的原理图还有吗?官方回复:有的,参见附件。

-

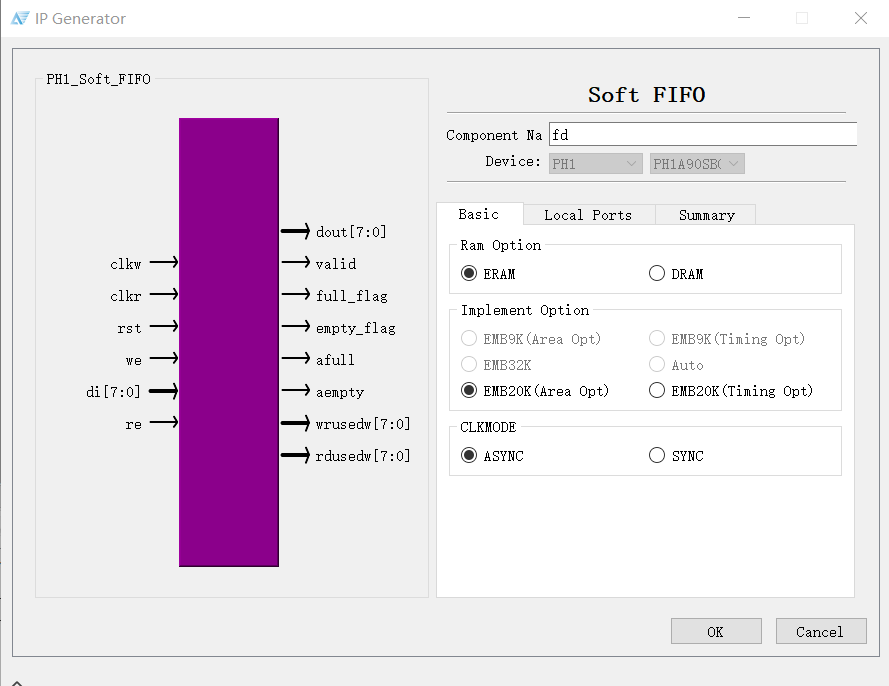

王如霖2023-11-13 14:46:17为什么 ramfifo ip核只有一个读写时钟官方回复:

王如霖2023-11-13 14:46:17为什么 ramfifo ip核只有一个读写时钟官方回复:您好,我们早期的FIFO只支持同步模式,所以只有一个时钟,在最新的软件中使用soft fifo已经支持异步模式。

-

孙唯俊2023-11-01 21:40:39请问在TD中怎么调出RTL图官方回复:

孙唯俊2023-11-01 21:40:39请问在TD中怎么调出RTL图官方回复:您好,请通过TD软件的菜单Tools>Schematic view>RTL Schematic打开RTL视图。

-

陈成2023-10-28 10:41:38如何获取ERAM的仿真模型官方回复:

陈成2023-10-28 10:41:38如何获取ERAM的仿真模型官方回复:您好,ERAM的仿真模型是直接存放在安装路径下的SIM目录的,但大多数模型都是加密了的,可能无法阅读和修改,感谢。

-

黄昊贤2023-10-27 15:32:16烧入程序检测不到外设 EZ-USB/FX2没有安装 找资源找不到 请问您有嘛官方回复:

黄昊贤2023-10-27 15:32:16烧入程序检测不到外设 EZ-USB/FX2没有安装 找资源找不到 请问您有嘛官方回复:您好,请问您有在设备管理器中安装下载器的驱动没?下载器的驱动位于安装路径下的driver目录。