FAQ专区

搜索

-

大类:

-

小类:

已选条件:

移除所有

-

TD软件是否支持verilog,VHDL,Verilog和VHDL混合编译?

支持。

-

安路工程怎么出一键式编译脚本?

首先按照正产流程将工程跑一遍,然后再选择TD软件界面Project->Export tcl file for the flow,就导出了一键式编译脚本。

具体可以参考TD软件手册,导出TCL脚本章节。

-

TD软件是否支持PLL、bram等的位置约束

支持,可以参考TD软件help下拉菜单中software userguide内容,约束例子如下:

set_inst_assignment {PLL_INST1} {location = x34y37z0;}

-

TD每次运行完后bit文件是否一致的?

安路的TD软件支持回溯特性,但也是有条件的:同一个操作系统版本、同一个TD软件版本、同样的Verilog/VHDL代码、同样的约束(adc、sdc)、同样的TD软件属性设置,这几个条件满足的话生成的bit文件是一致的。

-

安路CPLD可否提供内部时钟

EF2、EF3系列器件,内部集成了振荡器,可以输出时钟,中心频率约为266M,频率误差为30%。高精度场景不建议使用;

-

mslice超标该如何解决?

可以尝试打开TD,选择process->properties->Read Design->infer_add,调整该属性的开关。如果还没有解决,建议联系FAE。

-

PH1A100是否支持DDR3,DDR4

不支持

-

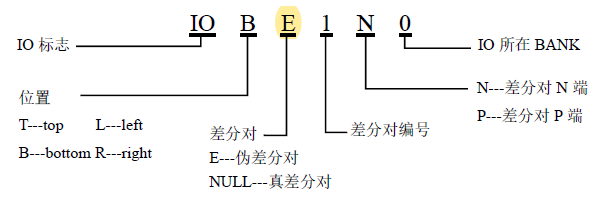

如何区分真差分和伪差分管脚?

管脚名字中带“E”的PN对是伪差分管脚,不带“E”的PN对是真差分。E表示Emulated。