FAQ专区

搜索

-

大类:

-

小类:

已选条件:

-

软件

移除所有

-

黄昊贤2023-10-27 15:32:16烧入程序检测不到外设 EZ-USB/FX2没有安装 找资源找不到 请问您有嘛官方回复:

黄昊贤2023-10-27 15:32:16烧入程序检测不到外设 EZ-USB/FX2没有安装 找资源找不到 请问您有嘛官方回复:您好,请问您有在设备管理器中安装下载器的驱动没?下载器的驱动位于安装路径下的driver目录。

-

田磊2023-08-14 16:27:57您好,目前我有一个贵司的AL-FPGA-LINK高速下载器,再安装了TD5.0软件中的驱动之后,出现了这样一个问题:“该设备无法启动(10),当前设备电源状态不能支持这个请求”。请问下出现这种情况的原因以及应当怎么解决?官方回复:

田磊2023-08-14 16:27:57您好,目前我有一个贵司的AL-FPGA-LINK高速下载器,再安装了TD5.0软件中的驱动之后,出现了这样一个问题:“该设备无法启动(10),当前设备电源状态不能支持这个请求”。请问下出现这种情况的原因以及应当怎么解决?官方回复:您好,您的这个报错可能原因是电脑的USB功耗限制配限制比较严格

可以试试在计算机管理-设备管理里

把USB Root Hub的节电模式关闭掉然后再测试看是否能够解决。

-

杨博2023-08-08 09:02:09我用midelsim联合TD仿真,拿pll锁相环ip测试可以,拿rom发现ip没有输出,检查sim_release发现里面没有rom的仿真模型文件,我换了个版本发现里面还是没有sim_release。安路TD都是这样吗?还是其他问题官方回复:

杨博2023-08-08 09:02:09我用midelsim联合TD仿真,拿pll锁相环ip测试可以,拿rom发现ip没有输出,检查sim_release发现里面没有rom的仿真模型文件,我换了个版本发现里面还是没有sim_release。安路TD都是这样吗?还是其他问题官方回复:您好,ROM的本质是使用了带初始化文件的ERAM来做的,所以仿真模型里也是使用的LOGIC_ERAM。不过我们的ROM由于模型原因,早期只支持网表仿真,要在较新的软件才支持源代码前仿,且要注意初始化文件的格式。

-

刘新宇2023-07-04 11:08:48请问TD软件是否能以命令行的方式实现下载功能?官方回复:

刘新宇2023-07-04 11:08:48请问TD软件是否能以命令行的方式实现下载功能?官方回复:您好,可以的,您可以参考TD软件UG,通过命令行形式启动TD软件,具体的下载命令可以从界面执行后,参考从console复制相应命令从命令行执行。

-

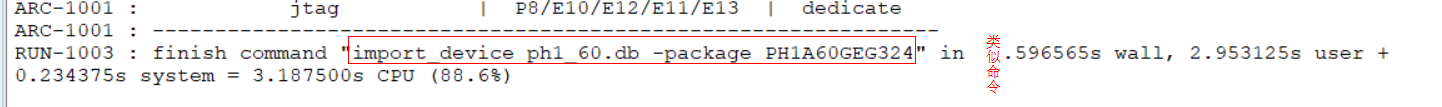

段彦亮2023-04-18 17:11:39最近看到TD软件官网有更新版本5.6.2,请问具体有哪些方面改进,是否提供下载权限。官方回复:

段彦亮2023-04-18 17:11:39最近看到TD软件官网有更新版本5.6.2,请问具体有哪些方面改进,是否提供下载权限。官方回复:您好,5.6.2主要是针对我们最近新宣布量产的SF1, PH1A90,PH1A180等器件的更新。如果使用这些器件可以跟相应的销售联系取得下载权限。如果是使用EF2/EG4/EF3等器件,则可以继续使用现有联系软件,无需更新。

-

Vapor2023-03-29 19:34:38错误Design emb exceeds是什么原因?如何解决?官方回复:

Vapor2023-03-29 19:34:38错误Design emb exceeds是什么原因?如何解决?官方回复:该提示指示用户使用ERAM资源数量超出本器件的最大值,用户可以减少ERAM使用数量或者更换规格更大的器件再次编绎。

-

孙国超2023-03-28 16:49:06在使用Chipwatcher时遇到错误:GUI-8501.Bit file code doesnot match with chipwatch's。请问这个错误出现的原因是什么?应该如何解决呢?官方回复:

孙国超2023-03-28 16:49:06在使用Chipwatcher时遇到错误:GUI-8501.Bit file code doesnot match with chipwatch's。请问这个错误出现的原因是什么?应该如何解决呢?官方回复:当下载到器件内部的位流与当前chipwatcher对应的工程不匹配时,会跳出上述提示。用户注意是否有在编绎完成后修改过CWC文件的动作;以及注意下载到板上的位流是否是当前对应工程编绎生成的。

-

Liu2023-03-17 21:48:27如何调用LVDS接口原语?官方回复:

Liu2023-03-17 21:48:27如何调用LVDS接口原语?官方回复:TD软件对于LVDS的支持不是通过原语来实现的,在.v/.hdl文件顶层和单端IO一样,在ADC引脚文件约束中选定P管脚对应的电平为LVDS/LVDS-E,TD软件会自动约束对应的N端管脚。