FAQ专区

搜索

-

大类:

-

小类:

已选条件:

-

软件

移除所有

-

TD支持哪些硬件描述语言,支持混合语言吗?

TD软件支持Verilog、VHDL、System Verilog,也支持这几种语言的混合编译。

-

网上下载的TD软件,安装后没有License文件,到哪里找?

安路软件一般自带6个月的免费License,如果没有License或有过期警告,可以再官网工具与资料下载->软件工具->TD License进行下载

-

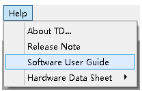

TD软件有使用指南吗?

TD软件安装后,会自带软件手册,可通过Help/Software User Guide菜单打开。

然后可打开全中文的软件使用手册。

-

时序约束文件SDC支持哪些约束?

SDC主要约束时钟信号、输入输出延时,伪路径约束等,图形界面下列出来的约束项TD软件都支持。

具体可参考TD软件附带的软件手册里时序约束章节。

-

物理约束文件ADC可做哪些约束?

ADC除了可约束用户IO的物理位置IO特性外还可以对片内物理单元(PLL,EMB、DSP等)和用户代码中具体单元进行位置约束。

具体可参考TD软件附带的软件手册里位置约束章节。

-

安路平台如何在Modelsim上做仿真?

在TD安装目录下的sim文件夹中包含了各个系列FPGA器件的行为模型描述文件,用户可自行在ModelSim里把描述文件编译为器件的库文件,然后在仿真时调用编译后的库文件即可。

支持RTL功能仿真和带延时的后仿真。

需要注意的是编写仿真激励需要调用glb()函数,具体可《 TD软件手册》,在TD菜单栏Help下拉菜单可直接打开。

-

ChipWatcher找不到信号怎么办?

找不到想看到的信号,可能是信号名未被继承或信号被优化了,可以在定义信号的地方添加keep综合指令避免该信号被优化或改名,例如 (*keep*) reg a; 或 reg a;//synthesis keep;

-

TD软件是否支持verilog,VHDL,Verilog和VHDL混合编译?

支持。