FAQ专区

-

EF2、EF3、EG4的加载时,对于时钟信号的质量要求,如JTAG加载的TCK,从串、从并加载的SCLK等有什么样的要求和建议。

时钟信号要求:边沿单调无回沟,从10%~90%小于10ns,建议在时钟源端串接一个33欧电阻,用于调整阻抗匹配,提高信号质量。

如果不能满足小于10ns的需求,需要打开引脚的Hysteresis(迟滞)功能。EF2 系列器件FPGA 中IOBB 管脚无法设置,Hysteresis 开关设置只存在于IOBE 类型管脚,其它器件IO 均为IOBE 类型,均可开启输入迟滞功能。

但是加载过程中TCK、SCLK的IO属性不能做配置调整,不支持Hysteresis(迟滞)功能,需要用户自行保证信号质量。

-

安路CPLD如何生成svf文件

点击菜单样tools选择 device chain,点击add按键,添加bit文件,之后点击creat svf,选择 svf for spi,点击ok 在工程目录下会生成一个al_devicechain的文件夹,生成的SVF文件保存在此文件夹下。

-

FIFO IP与RAMFIFO IP有何不同?

FIFO IP是使用了BRAM块内嵌的硬件FIFO控制硬核,不需要额外消耗LUT资源;

RAMFIFO IP的FIFO控制器是由LUT资源搭建的,属于软核,该IP主要为了解决FIFO IP没有引出指示FIFO中还有多少数据的rdusedw、wrusedw参数。

-

JTAG链支持多少级?

JTAG级联本身没有限制,但从实际应用上,为了满足JTAG信号和时序的要求,一般不能超过10级。

备注:如果级联时需要擦写存储位流的Flash,EF2、EG4、AL3器件必须放置在JTAG链路的前三级。

-

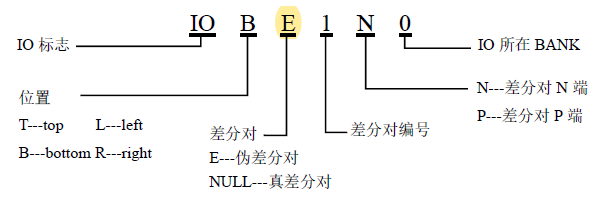

如何区分真差分和伪差分管脚?

管脚名字中带“E”的PN对是伪差分管脚,不带“E”的PN对是真差分。E表示Emulated。

-

EF2、EF3、EG4、AL3系列 差分输入管脚内部有100欧姆匹配电阻吗?

首先要看IO类型,支持真差分的IO内部具有100欧姆匹配电阻,而伪差分IO内部没有匹配电阻。具体请参考各个器件的Datasheet。

备注1:真差分IO可配置使用内部匹配,也可以外部匹配。

备注2:差分输入摆幅超过500mv,必须使用外部匹配电阻。

-

EF2/ EF3/EG4系列产品是否可以支持单电源供电

EF2/EF3 系列可以支持,但是单电源VCCAUX供电电压要大于等于2.5V,EG4系列不支持单电源供电,需要1.2V的核电压。

-

IOBB类型的IO需要注意什么

EF2系列器件、EF3L15、EF3L25器件的一部分IO属于IOBB类型,使用建议如下:

1. 做输出时,驱动电流和SlewRate不可调节,建议输出信号线预留串阻。

2. 做输入时,不建议接入时钟信号,尤其是上升沿较缓(20%~80%超过10ns)的时钟信号。如果是慢速变化的信号,可以接到IOBB,但建议逻辑用时钟采样一拍再使用。